#

# High-Speed Planar GaAs Nanowire Arrays with $f_{max} > 75$ GHz by Wafer-Scale Bottom-up Growth

Xin Miao,<sup>†,§</sup> Kelson Chabak,<sup>†,‡,§</sup> Chen Zhang,<sup>†</sup> Parsian K. Mohseni,<sup>†</sup> Dennis Walker, Jr.,<sup>‡</sup> and Xiuling  $Li^{*,\dagger}$

<sup>†</sup>Micro and Nanotechnology Laboratory, University of Illinois Urbana–Champaign, 208 N. Wright Street, Urbana, Illinois 61801, United States

<sup>‡</sup>Air Force Research Laboratory, Sensors Directorate, 2241 Avionics Circle, Wright-Patterson Air Force Base, Ohio 45433, United States

Supporting Information

**ABSTRACT:** Wafer-scale defect-free planar III–V nanowire (NW) arrays with ~100% yield and precisely defined positions are realized via a patterned vapor–liquid–solid (VLS) growth method. Long and uniform planar GaAs NWs were assembled in perfectly parallel arrays to form double-channel T-gated NW array-based high electron mobility transistors (HEMTs) with DC and RF performance surpassing those for all field-effect transistors (FETs) with VLS NWs, carbon nanotubes (CNTs), or graphene channels in-plane with the substrate. For a planar GaAs NW array-based HEMT with 150 nm gate

length and 2 V drain bias, the on/off ratio  $(I_{ON}/I_{OFF})$ , cutoff frequency  $(f_T)$ , and maximum oscillation frequency  $(f_{max})$  are 10<sup>4</sup>, 33, and 75 GHz, respectively. By characterizing more than 100 devices on a 1.5 × 1.5 cm<sup>2</sup> chip, we prove chip-level electrical uniformity of the planar NW array-based HEMTs and verify the feasibility of using this bottom-up planar NW technology for post-Si large-scale nanoelectronics.

**KEYWORDS:** Bottom-up, VLS, nanowire, III-V, transistor, VLSI

• o increase transistor density and improve circuit performance, the semiconductor chip industry has been driven to constantly scale down critical feature sizes in transistors. As the scaling continues, severe short channel effects (SCE) forfeit performance gains via pure dimensional down-scaling.<sup>1</sup> New transistor architectures and materials are needed to boost the performance with further down-scaling.<sup>1,2</sup> Si-based trigate and ultrathin-body transistors have demonstrated superior electrostatics and enhanced carrier mobility compared to traditional bulk Si technology.<sup>3,4</sup> III–V nanowires (NWs), carbon nanotubes (CNTs), and graphene are under extensive research for possible uses in post-Si transistor technology because they all have inherent three-dimensional (3D) or ultrathin structures for SCE control and possess much greater carrier mobility than Si.<sup>2,5-7</sup> Good electrostatics and high carrier mobility are also beneficial for the intrinsic gain  $(G_m/G_{ds})$ , where  $G_m$  is the transconductance and  $G_{ds}$  is the output conductance),<sup>8</sup> enabling analog/RF features for system-on-chip (SOC) applications.<sup>4,9</sup> Although some CNTs have finite band gaps, synthesizing 100% semiconductor CNTs with uniform diameters and placing them precisely in high density on a wafer has proven difficult for large-scale integrated circuit (IC) applications.<sup>6</sup> Alternatively, the synthesis of wafer-scale singlecrystal monolayer graphene seems feasible for large-scale applications, but digital ICs cannot be built on graphene due to its metal-like band structure.<sup>7,10</sup> In contrast, III–V NWs have

well-defined and tunable bandgaps (via composition modulation), and can be fabricated in large-scale with precise site-control.<sup>2,5</sup> Therefore, III–V NWs are the most promising candidates for post-Si SOC applications.

Vertical III-V NW field-effect transistors (FETs) have been demonstrated with site-controlled III-V NW channels defined by top-down dry etching,<sup>11</sup> selective area epitaxy (SAE),<sup>12</sup> and vapor–liquid–solid (VLS) bottom-up methods.<sup>13–15</sup> However, the vertical device layout makes vertical NW FETs incompatible with mainstream planar processing. Vertical NW FETs also have more issues with parasitic resistance and capacitance compared to planar NW FETs. Thus, planar NW FETs are preferable for high-performance digital and RF applications. There have been many studies on planar III-V NW FETs fabricated through the top-down dry etching approach.<sup>16–19</sup> The top-down approach requires complex patterning techniques and introduces damage and defects in the NWs. Bottomup III-V NWs are made from constructive methods and are supposed to have much better material quality.<sup>20</sup> However, the SAE method has an even higher level of processing complexity comparing with the top-down dry etching approach.<sup>21</sup> The

Received:September 18, 2014Revised:November 22, 2014Published:December 10, 2014

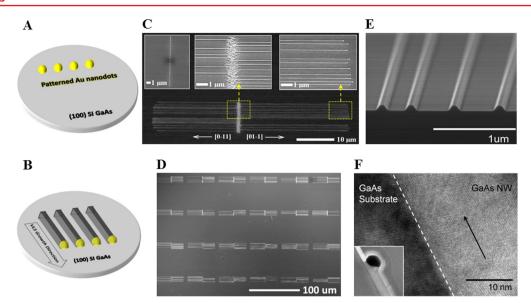

**Figure 1.** Planar GaAs NW arrays. (A) Au seeds are formed by EBL, Au evaporation, and lift-off processes. (B) VLS growth of planar GaAs NWs in parallel arrays on SI GaAs substrates. (C) Tilt-view SEM image of a representative planar GaAs NW array with 100% planar NW yield. The planar NWs grow bidirectionally in the antiparallel  $[0\overline{1}1]$  and  $[01\overline{1}]$  directions. Insets, from the left to the right, show the patterned Au seeds, the dividing line between the oppositely propagated NWs and the near-tip portions of the  $[01\overline{1}]$  planar NWs. (D) Top-view SEM image of 4 × 6 planar GaAs NW arrays, illustrating the wafer-scale growth capability. (E) Tilt-view SEM image of a cleaved planar GaAs NW array. The planar NWs have perfectly uniform trapezoidal cross sections. (F) HR-TEM image of a representative planar GaAs NW liberated from the as-grown sample (the black arrow indicates the NW growth direction), showing its defect-free and zinc-blende construction. The inset highlights the cross-sectional geometry of the Au nanoparticle relative to the NW and substrate.

morphologies of SAE planar III-V NWs have strong dependence on the top-down patterning profiles of the SAE templates, which can lead to nonuniform SAE NWs. VLS III-V NWs grown from patterned Au seeds require much less patterning efforts (requiring a dot pattern instead of a line) and prove to have very uniform morphologies.<sup>5</sup> Because the sizes of VLS III-V NWs are determined by the volumes of the Au seeds, VLS NWs can have feature sizes smaller than what the patterning can offer. Given the fact that VLS III-V NWs prefer to grow in the (111)B directions,<sup>22</sup> only VLS vertical III-V NW arrays have been demonstrated using III-V (111)B substrates.<sup>13-15</sup> In order to make planar NW FETs, many postgrowth alignment methods have been developed to align the as-grown vertical III-V NWs in-plane with the substrates such as contact printing,<sup>23</sup> field-assisted,<sup>24</sup> blown bubble,<sup>25</sup> combing,<sup>26</sup> sliding,<sup>27</sup> Langmuir–Blodgett,<sup>28</sup> microfluidics,<sup>29,30</sup> or dielectrophoresis.<sup>31,32</sup> Aside from the additional processing complexity involved in these alignment processes, none of them have the precise NW positioning capability required for making large-scale ICs. So far, the best planar III-V NW FETs fabricated by aligning VLS vertical InAs NWs in-plane with the substrates report  $f_{\text{max}} = 1.8$  GHz, which is far less than its high mobility would predict.33

VLS planar NWs have an epitaxial relation with the host substrates and are fully compatible with mainstream planar processing.<sup>34</sup> Our group first reported the controlled VLS growth of  $\langle 110 \rangle$  planar GaAs NWs on semi-insulating (SI) (100) GaAs substrates using randomly dispersed Au colloids as the growth seeds.<sup>34</sup> Using this growth method, planar GaAs NW metal—semiconductor FETs (MESFETs), high electron mobility transistors (HEMTs), and metal—oxide—semiconductor FETs (MOSFETs) were demonstrated with good DC characteristics.<sup>20,35–38</sup> However, the random distribution of the dispersed Au colloids prevents the realization of large-scale ICs using these planar GaAs NW FETs. Growing from top-down

patterned Au seeds, VLS planar ZnO NW arrays on R-plane sapphire substrates were achieved.<sup>39</sup> However, due to the nonideal NW quality, the performance of the FETs made from the ZnO NW arrays is far below what is needed for post-Si ICs. Similar work using ZnO VLS NW arrays on *c*-plane GaN and GaN on (0001) sapphire was also demonstrated with more than two crystallographic directions, which makes parallel arrays challenging.<sup>40,41</sup>

In this paper, we report a major milestone to realize waferscale defect-free VLS planar III–V NW arrays with ~100% yield and precisely defined positions. For the first time, planar NW array-based HEMTs are demonstrated with recordbreaking DC and RF performances among planar FETs with VLS NWs, CNTs, or graphene channels. This work verifies the feasibility of using our bottom-up planar NW technology for post-Si large-scale nanoelectronics and brings the bottom-up nanotechnology a large step forward toward real-world applications.

Growth of Planar NW Arrays. The growth of wafer-scale planar GaAs NW arrays, as illustrated in Figure 1A,B, begins by patterning arrays of Au seeds. Arrays of Au seeds (disk-shape) with diameters of 50 to 300 nm, center-to-center pitch of 100 to 500 nm and a uniform height of 50 nm were formed on SI (100) GaAs substrates via electron beam lithography (EBL), Au evaporation and lift-off processes. The feature sizes of the NWs can be smaller than the EBL pattern sizes if a thin enough Au evaporation is used because the volume of the Au seed determines the NW size. Because VLS planar NWs have an epitaxial relation with the substrates, stringent sample cleaning procedures were applied after Au seed deposition and before the VLS growth to ensure high planar NW yield. The VLS NW growth was carried out in an Aixtron 200/4 metal-organic chemical vapor deposition (MOCVD) reactor using a twotemperature-step (450  $\rightarrow$  435 °C) growth method (see Methods).<sup>37</sup> Figure 1C shows a tilt-view scanning electron

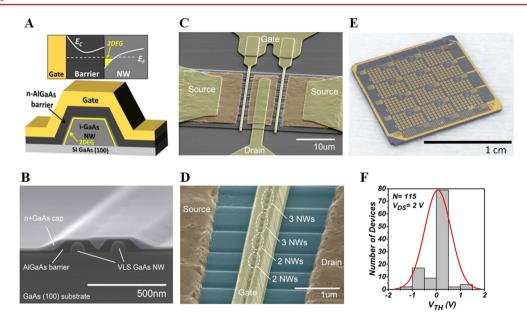

**Figure 2.** Planar NW array-based HEMTs. (A) Illustration of the operation mechanism of planar NW array-based HEMTs. (B) Cross-section of the planar NW heterostructure with two identical GaAs NWs sharing the  $Al_{0.33}Ga_{0.67}As$  barrier. (C) Tilt-view false-color SEM image of a representative fully fabricated planar NW array-based HEMT with  $L_G = 150$  nm and 30 planar GaAs NWs spanning across both channels. (D) Magnified false-color SEM image of the device's (shown in C) channel region. (E) Optical image of a fully fabricated 1.5 × 1.5 cm<sup>2</sup> device chip with 115 precisely positioned planar NW array-based HEMTs. (F) Histogram and Gaussian distribution of the 115 devices and threshold voltage extrapolated by a tangent line from  $I_{DS}$  at peak transconductance condition to  $I_{DS} = 0$  V at  $V_{DS} = 2$  V.

microscope (SEM) image of a representative planar GaAs NW array with 100% planar NW yield. The planar GaAs NWs grow bidirectionally in the antiparallel  $[0\overline{1}1]$  and  $[01\overline{1}]$  directions, with respective lengths of  $\sim$ 22 and 28  $\mu$ m for the 140 s growth. The origin of the difference in growth rate for the two presumably crystallographically equivalent directions is under further study. Because of the bidirectionality, the grown NWs are no longer equally spaced; wherever there are missing NWs in the array propagating to one side, they can be surely found on the other side. The insets of Figure 1C, from the left to the right, show the patterned Au seeds, the dividing line between the oppositely propagated NWs and the near-tip portions of the  $[01\overline{1}]$  planar NWs. The tiny out-of-plane GaAs whiskers at the dividing line are originated from tiny Au particles split from the patterned Au seeds. Figure 1D is the top-view SEM image of 4  $\times$  6 planar GaAs NW arrays on the same sample illustrating the wafer-scale growth capability. The probabilities of planar GaAs nanowires growing in the  $[0\overline{1}1]$  and  $[01\overline{1}]$  directions are about equal because the  $[0\overline{1}1]$  and  $[01\overline{1}]$  directions are crystallographically equivalent.<sup>42</sup> The tilt-view SEM image of a cleaved planar GaAs NW array in Figure 1E shows that the planar GaAs NWs grown from the patterned seeds have perfectly uniform trapezoidal cross sections. High-resolution transmission electron micrograph (HR-TEM) analysis (see Supporting Information) of a representative planar NW liberated from the as-grown sample reveals a purely zinc-blende NW crystal structure, entirely free of twin-defects and stacking faults, with VLS growth along the  $\langle 110 \rangle$  direction. Figure 1F shows the HR-TEM image of the planar NW and substrate interface (the black arrow indicates the NW growth direction). The inset shows a reduced magnification image that highlights the crosssectional geometry of the Au nanoparticle (dark contrast) relative to the NW and substrate.

Growth and Fabrication of Planar NW Array-Based HEMTs. To explore the electronic properties of the planar NW arrays, a  $1.5 \times 1.5$  cm<sup>2</sup> device chip with 115 planar NW arraybased HEMTs in repeating reticles was fabricated for DC/RF characterization. The 115 planar NW array-based HEMTs have various gate lengths and device widths. Au seed arrays were first formed on the SI (100) GaAs substrate in accordance with the mask layout design. Bidirectional (110) planar GaAs NW arrays were then grown for 200 s using the same growth conditions as mentioned above. Upon the cessation of the VLS NW growth, the reactor temperature was raised to 680 °C and pressure was lowered to 100 mbar to grow in situ conformal epitaxial layers comprised of a 3 nm undoped  $Al_{0.33}Ga_{0.67}As$  spacer, a 50 nm Sidoped (3  $\times$  10  $^{18}$  cm  $^{-3})$  Al\_{0.33}Ga\_{0.67}As barrier layer, and a 50 nm  $n^+$  (5 × 10<sup>18</sup> cm<sup>-3</sup>) GaAs ohmic contact layer. As illustrated in Figure 2A, the operation of a planar NW array-based HEMT relies on the gate's modulation of the two-dimensional electron gas (2DEG) formed at the heterointerfaces between the AlGaAs barrier and the GaAs NW sidewall and top facets.35 Therefore, a conformal Al<sub>0.33</sub>Ga<sub>0.67</sub>As barrier wrapping over the NWs is critical for good device performance. High background H<sub>2</sub> flow was adopted during the barrier growth, which effectively reduced the Al<sub>0.33</sub>Ga<sub>0.67</sub>As growth rate and promoted better barrier coating. Figure 2B shows the cross-section of the planar NW heterostructure with two identical GaAs NWs sharing the Al<sub>0.33</sub>Ga<sub>0.67</sub>As barrier. Because the growth substrate is semi-insulating, no conduction occurs at the heterointerfaces between the Al<sub>0.33</sub>Ga<sub>0.67</sub>As and the GaAs substrate. This was confirmed by characterizing a control device with no NW in the channel (see Supporting Information).

The device fabrication is fully compatible with the planar processing (see Methods). The NWs can be aligned to the mask sets with combinations of EBL and optical lithography. Between the bidirectional planar NW arrays, the relatively longer  $[01\overline{1}]$  arrays (~35  $\mu$ m) were chosen for device processing. Because the  $[0\overline{1}1]$  and  $[01\overline{1}]$  planar NWs have the same sizes, crystal quality (defect-free), and NW sidewall

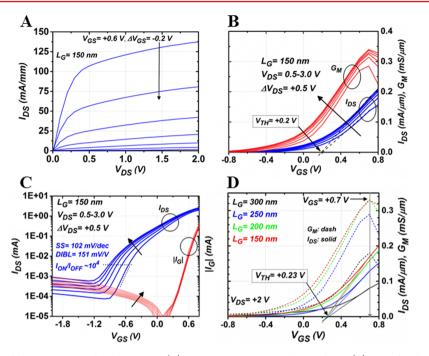

Figure 3. DC characteristics of planar NW array-based HEMTs. (A) Output current versus drain voltage. (B) Transfer characteristics as a function of gate and drain voltage. (C) Log gate and drain current versus gate and drain voltage. (D) Extraction of threshold voltage for the four fabricated gate lengths.

and top facets, they have the same electrical properties.<sup>35</sup> The long  $[01\overline{1}]$  planar NW arrays allowed the use of a two-finger Tgated RF pad layout where both gates share the same NWs. A representative fully fabricated device with  $L_{\rm G}$  = 150 nm and 30 planar GaAs NWs spanning across both channels is shown in Figure 2C. Figure 2D is a magnification of the channel region showing all three transistor terminals. It should be noted that NWs in the ungated regions in Figure 2D appear merged. This is because the shared thick n<sup>+</sup> GaAs cap layer buries the original corrugated NWs, as is illustrated in Figure 2B. However, the actual number of NWs can be specified in the center of the Tgate where the n<sup>+</sup> GaAs cap is wet-etched down to the Al<sub>0.33</sub>Ga<sub>0.67</sub>As barrier layer. Figure 2E shows the fully fabricated device chip with 115 precisely positioned planar NW arraybased HEMTs. Owing to the excellent structural uniformity, the NW HEMTs have excellent electrical uniformity. For example, the histogram (Figure 2F) showing the extracted threshold voltage  $(V_{TH})$  at  $V_{DS}$  = 2 V illustrates good distribution centered at the designed  $V_{\text{TH}}$  (~0 V). By using optimized gate recess etching, even better electrical uniformity can be achieved.

**Electrical Characterization and Discussion.** The DC current–voltage (I-V) characteristics of a two-finger planar NW array-based HEMT with  $L_{\rm G} = 150$  nm (as shown in Figure 2C) are plotted in Figure 3A–C. Normalized results are based on the top and two-sidewall NW periphery under the T-gate  $(W_{\rm NW} = 75 + 75 + 60 = 210 \text{ nm})$ . Because there are 30 NWs spanning across both channels, the total device width is 12.6  $\mu$ m ( $2 \times 30 \times 0.21 \mu$ m). The output I-V performance shows excellent saturation at low-bias where a maximum transconductance  $(G_{\rm m,max})$  is achieved (Figure 3A). Shown in the transfer characteristics (Figure 3B), the  $V_{\rm TH}$  was extracted by a tangent  $I_{\rm DS}$  line at  $G_{\rm m,max}$  and extrapolated to  $I_{\rm DS} = 0$ , which is approximately +0.2 V, indicating enhancement mode operation. In Figure 3C, subthreshold slope, SS = 102 mV/dec, and drain-induced barrier lowering, DIBL = 151 mV/V, were extracted

along with on/off ratio  $(I_{\rm ON}/I_{\rm OFF}) \sim 10^4$ . In Figure 3D, the linear transfer performance over four studied gate lengths indicates a uniform  $G_{\rm m,max}$  gate bias and  $V_{\rm TH}$  = +0.23 V, which can be interpreted as negligible SCE in this  $L_{\rm G}$  range.

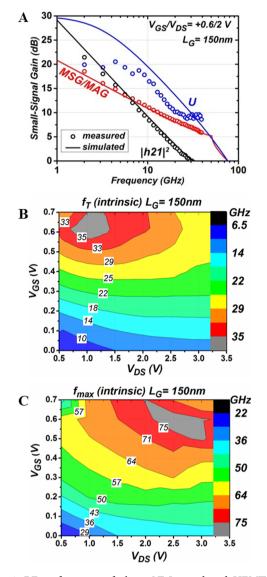

Small-signal RF performance was characterized in the 0.1-40 GHz range for each  $L_{\rm G}$  shown in Figure 3D. The best deembedded frequency performance,  $f_T/f_{max} \sim 33/75$  GHz, was obtained with  $L_{\rm G}$  = 150 nm measured at  $V_{\rm DS}$  = 2 V with 30 NWs spreading along a 20  $\mu$ m contact width—a NW density of  ${\sim}1.5$  NWs/ ${\mu}m$  (see Supporting Information). To our knowledge, this is the highest reported  $f_{\rm max}$  achieved on any nanoscale device with VLS NWs, CNTs, or 2D sheets aligned in-plane with the substrate.<sup>7,33,43-45</sup> Representative gain versus frequency RF measurements are shown in Figure 4A for  $L_{\rm G}$ = 150 nm and  $V_{\rm GS}/V_{\rm DS}$  = +0.6/2.0 V. The short-circuit current gain  $(H_{21})$  decreases by -20 dB/dec and falls to 0 dB at  $f_T = 33$ GHz. The maximum available gain (MAG) and unilateral gain (U) are both plotted and extracted to  $f_{\rm max}{=}$  75 GHz using a conventional small-signal circuit model (see Supporting Information). As expected, the power gains (MAG, U) are well above  $H_{21}$  which is indicative of the excellent electrostatics. In Figure 4B,C, the  $f_{\rm T}$  and  $f_{\rm max}$  at  $L_{\rm G}$  = 150 nm are mapped for various gate and drain bias, respectively. The peak  $f_{\rm T}$  occurs at lower drain voltage where  $G_{m,max}$  is reached without introducing hot-electron effects. The peak  $f_{\text{max}}$  performance shifts slightly toward high  $V_{\rm DS}$  because of its higher sensitivity to gate-todrain capacitance. In addition,  $G_{\rm m}$  from the 3D NW channel remains high once  $V_{\rm DS}$  saturates (~1 V); therefore, a high  $f_{\rm T}/$  $f_{\rm max} \sim 37/67$  GHz was measured at  $V_{\rm GS}/V_{\rm DS}$  = +0.6/1 V, which is enticing for applications demanding high gain with small power consumption.

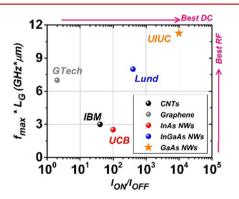

Benchmarked against the best planar FETs built with VLS NWs, CNTs, or graphene channels, our planar NW array-based HEMT has superior  $f_{\rm max}L_{\rm G}$  as well as the highest  $I_{\rm ON}/I_{\rm OFF}$  (Figure 5). It should be noted that the high  $f_{\rm max}L_{\rm G}$  was obtained despite having large parasitic capacitance. Analyzing

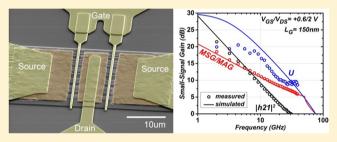

**Figure 4.** RF performance of planar NW array-based HEMTs. (A) Measured and simulated small signal gain versus frequency for  $L_G = 150 \text{ nm}$  and  $V_{\rm DS} = 2 \text{ V}$ . Contour plots of  $f_{\rm T}$  (B) and  $f_{\rm max}$  (C) as a function of gate and drain voltage for  $L_{\rm G} = 150 \text{ nm}$ .

**Figure 5.** DC and RF performance benchmark of the best planar FETs built with VLS NWs, CNTs, or graphene channels evaluated by  $I_{\rm ON}/I_{\rm OFF}$  and  $f_{\rm max}L_{\rm G}$ . The planar NW array-based HEMT ranks among the best reported in literature.

with an equivalent circuit small-signal model (see Supporting Information), we found the intrinsic gate-to-channel capacitance accounts for only 17% of the total gate capacitance. Eliminating the parasitic capacitance, we extracted a high intrinsic velocity of  $\sim 1.49 \times 10^7$  cm/s (at  $V_{\rm DS} = 1$  V), which yields speed exceeding 0.3 THz (see Supporting Information). The large parasitic capacitance is attributed to the low NW density (~1.5 NWs/ $\mu$ m), which can be largely reduced by enabling the unidirectional planar NW growth and using a tight NW pitch.<sup>46</sup> In our previous study using randomly dispersed Au colloids as the growth seeds, unidirectional planar GaAs  $\rm NWs^{42}$  and planar NWs with sub-50 nm sizes and sub-20 nm pitches have all been demonstrated.<sup>37</sup> Thus, given finer patterning, high-density unidirectional planar NW arrays should be a viable option in the future to reduce parasitic capacitance. By using smaller planar NWs in the channel and thinner barrier layer with sufficient delta doping, the dimensions of the devices, such as  $L_{G}$  and source-to-drain separation, can be down-scaled while maintaining good electrostatics. With future iterations such as high-k dielectric gate integration and growth enablement of planar In(Ga)As NW arrays,47 our bottom-up planar NW technology has a clear roadmap to meet both the digital and RF requirements for future SOC applications.

Conclusions and Remarks. Through the demonstration of wafer-scale planar GaAs NW arrays with ~100% yield and precise NW site and size control, we have provided evidence that our planar NW technology is a viable option for large-scale electronic device applications. For the first time, planar NW technology was used to demonstrate array-based HEMTs with large number of identical GaAs NWs self-assembled in-plane with the substrate and sufficiently long for double-channel RF device fabrication. Benchmarking against the existing planar FETs with VLS NWs, CNTs, or graphene channels, our planar NW array-based HEMTs show the best DC  $(I_{ON}/I_{OFF})$  and RF  $(f_{\max}L_G)$  performances, despite the unoptimized device layout. The excellent device metrics are not only obtainable from a hero device but from the majority of the 115 devices on a 1.5  $\times$ 1.5 cm<sup>2</sup> device chip. Our planar NW technology overcomes the ubiquitous challenge of aligning III-V NWs or CNTs with deterministic positions in-plane with the substrates, and is well positioned for post-Si large-scale nanoelectronics.

Methods. Growth of Planar NW Array-Based HEMTs. Prior to the MOCVD growth, alignment markers were etched into the SI (100) GaAs substrates using a PlasmaTherm 770 inductively coupled plasma (ICP) etching system with an optically defined pattern and AZ-5214 photoresist as the etch mask. The ICP etch settings were BCl<sub>2</sub>/Cl<sub>2</sub>/Ar 10/5/5 sccm at 150 W. Then, Au seeds with 100 nm diameter, 300 nm centerto-center separation and 30 nm height were formed by EBL, Au deposition (30 nm) and lift-off processes. A stringent cleaning process of repeating 10 min soaks in PG remover solvent was carried out before loading the sample in an Aixtron 200/4 MOCVD reactor. Trimethyl-gallium (TMGa), trimethylaluminum (TMAl), AsH<sub>3</sub>, and Si<sub>2</sub>H<sub>6</sub> were used as the precursors for Ga, Al, As, and Si. Oxide desorption was carried out at 625  $^\circ\text{C}$  for 10 min with AsH33 overpressure. The reactor pressure and temperature were then brought to 950 mbar and 450 °C for VLS NW growth. Constant flows of 10-sccm TMGa  $(1.16 \times 10^{-4} \text{ mol/min})$  and 10 sccm AsH<sub>3</sub>  $(4.46 \times 10^{-4} \text{ mol/})$ min) were used in the 200 s VLS GaAs NW growth. In the NW growth, reactor temperature was initially kept at 450 °C for 20 s, then dropped linearly to 430 °C in 60 s and maintained at 430  $^\circ\text{C}$  for another 120 s. With such two-temperature-step VLS growth method, planar GaAs NW arrays with ~100% yield and high crystal quality were achieved. After the VLS NW growth,

the reactor pressure was adjusted to 100 mbar; and reactor temperature was elevated for epitaxial thin film growth. A 3 nm undoped  $Al_{0.33}Ga_{0.67}As$  layer was grown at 500 °C to stabilize the surface atoms of GaAs NWs and preserve NWs' original 3D morphology from the following high temperature growth. The 50 nm Si-doped (3 × 10<sup>18</sup> cm<sup>-3</sup>)  $Al_{0.33}Ga_{0.67}As$  barrier layer and 50 nm n<sup>+</sup> (5 × 10<sup>18</sup> cm<sup>-3</sup>) GaAs ohmic contact layer were grown at 680 °C for high doping efficiency.

Fabrication of Planar NW Array-Based HEMTs. Ohmic contacts were deposited using an EBL pattern and metal evaporation and lift-off of Ni/Ge/Au/Ni/Au. The sample was alloyed at 400 °C for 20 s in hydrogen in a lab-built annealing system. Next, an optically defined mesa wet-etch step using  $H_2SO_4/H_2O_2/H_2O$  (1:8:80) for 20 s was achieved. The pad metal was deposited using optical lithography, metal evaporation, and lift-off of Ti/Au. The next step was EBL of the T-gate which consisted of exposing and developing a trilayer PMMA/MMA/PMMA resist stack. Finally, gate recess etching was done in citric acid/ $H_2O_2$  (4:1) for 7 s and followed by metal evaporation and lift-off of Ti/Pt/Au.

DC/RF Characterization of Planar NW Array-Based HEMTs. RF measurements were performed using reticle step automation on a Cascade Microtech probe station with Agilent Technologies E8364B network analyzer with bias tees connecting to a semiconductor parametric analyzer. Off-chip short-open-load-thru calibration was used to de-embed up to the probe tips while on-wafer open and short structures were used to de-embed the device pad capacitance. The RF settings were -27 dBm input power and the frequency range was 0.01-40 GHz.

TEM Characterization of Planar NWs. Lamellae for TEM analysis containing single planar NWs were prepared using an FEI Helios NanoLab 600i FIB. HR-TEM characterization was carried out using a JEOL 2010F EF-FEG instrument.

# ASSOCIATED CONTENT

#### **S** Supporting Information

High-resolution transmission electron microscopy, supplemental static and radio frequency (RF) electrical characterization, and a small-signal RF model. This material is available free of charge via the Internet at http://pubs.acs.org.

## AUTHOR INFORMATION

#### **Corresponding Author**

\*E-mail: xiuling@illinois.edu.

#### **Author Contributions**

<sup>§</sup>X.M. and K.C. contributed equally.

#### Notes

The authors declare no competing financial interest.

## ACKNOWLEDGMENTS

The authors acknowledge support of this work by National Science Foundation ECCS 1001928 (X.M., K.C., and X.L.) and DMR 1006581 (C.Z. and X.L.), Office of Naval Research (ONR N000141110634, P.K.M. and X.L.) and Air Force Research Laboratory, Sensors Directorate (K.C. and D.W.). TEM characterization and sample preparation via FIB were carried out in part in the Frederick Seitz Materials Research Laboratory Central Research Facilities, University of Illinois.

# REFERENCES

(1) Ferain, I.; Colinge, C. A.; Colinge, J.-P. Nature 2011, 479 (7373), 310–316.

(2) Del Alamo, J. A. Nature 2011, 479 (7373), 317-323.

(3) Auth, C. In 22-nm fully-depleted trigate CMOS transistors; IEEE Custom Integrated Circuits Conference, San Jose, CA, Sept 9–12, 2012; IEEE: Bellingham, WA, 2012; pp 1–6.

(4) Cheng, K.; Khakifirooz, A.; Kulkarni, P.; Ponoth, S.; Haran, B.; Kumar, A.; Adam, T.; Reznicek, A.; Loubet, N.; He, H. In *ETSOI CMOS for system-on-chip applications featuring 22nm gate length, sub-100nm gate pitch, and 0.08μm 2 SRAM cell*; 2011 Symposium on VLSI Technology (VLSIT), Honolulu, HI, June 15–17, 2011; IEEE: Bellingham, WA, 2011; pp 128–129.

(5) Wernersson, L.-E.; Thelander, C.; Lind, E.; Samuelson, L. Proc. IEEE 2010, 98 (12), 2047–2060.

(6) Rutherglen, C.; Jain, D.; Burke, P. Nat. Nanotechnol. 2009, 4 (12), 811–819.

(7) Wu, Y.; Jenkins, K. A.; Valdes-Garcia, A.; Farmer, D. B.; Zhu, Y.; Bol, A. A.; Dimitrakopoulos, C.; Zhu, W.; Xia, F.; Avouris, P. *Nano Lett.* **2012**, *12* (6), 3062–3067.

(8) Subramanian, V.; Parvais, B.; Borremans, J.; Mercha, A.; Linten, D.; Wambacq, P.; Loo, J.; Dehan, M.; Gustin, C.; Collaert, N. *IEEE Trans. Electron Devices* **2006**, *53* (12), 3071–3079.

(9) Jan, C.-H.; Bhattacharya, U.; Brain, R.; Choi, S.-J.; Curello, G.; Gupta, G.; Hafez, W.; Jang, M.; Kang, M.; Komeyli, K. In A 22nm SoC platform technology featuring 3-D tri-gate and high-k/metal gate, optimized for ultra low power, high performance and high density SoC applications; 2012 IEEE International Electron Devices Meeting (IEDM); IEEE: Bellingham, WA, 2012; pp 3.1. 1–3.1. 4.

(10) Lee, J.-H.; Lee, E. K.; Joo, W.-J.; Jang, Y.; Kim, B.-S.; Lim, J. Y.; Choi, S.-H.; Ahn, S. J.; Ahn, J. R.; Park, M.-H. Science **2014**, 344 (6181), 286–289.

(11) Zhao, X.; Lin, J.; Heidelberger, C.; Fitzgerald, E. A.; del Alamo, J. A. In *Vertical nanowire InGaAs MOSFETs fabricated by a top-down approach*; 2013 IEEE International Electron Devices Meeting (IEDM), Washington, DC, Dec. 9–11, 2013; pp 28.4.1–28.4.4.

(12) Tomioka, K.; Yoshimura, M.; Fukui, T. Nature 2012, 488 (7410), 189–192.

(13) Egard, M.; Johansson, S.; Johansson, A.-C.; Persson, K.-M.; Dey, A.; Borg, B.; Thelander, C.; Wernersson, L.-E.; Lind, E. *Nano Lett.* **2010**, *10* (3), 809–812.

(14) Persson, K.-M.; Berg, M.; Borg, M. B.; Wu, J.; Johansson, S.; Svensson, J.; Jansson, K.; Lind, E.; Wernersson, L.-E. *IEEE Trans. Electron Devices* **2013**, *60* (9), 2761–2767.

(15) Johansson, S.; Memisevic, E.; Wernersson, L. E.; Lind, E. *IEEE Electron Device Lett.* **2014**, 35 (5), 518–520.

(16) Wu, Y.; Wang, R.; Shen, T.; Gu, J.; Ye, P. In First experimental demonstration of 100 nm inversion-mode InGaAs FinFET through damage-free sidewall etching; 2009 IEEE International Electron Devices Meeting (IEDM), Baltimore, MD, Dec 7–9, 2009; IEEE: Bellingham, WA, 2009; pp 1–4.

(17) Gu, J.; Liu, Y.; Wu, Y.; Colby, R.; Gordon, R. G.; Ye, P. D. Proc IEEE Int. Electron Devices Meet. 2011, 33.2.1-4.

(18) Radosavljevic, M.; Dewey, G.; Basu, D.; Boardman, J.; Chu-Kung, B.; Fastenau, J.; Kabehie, S.; Kavalieros, J.; Le, V.; Liu, W. In Electrostatics improvement in 3-D tri-gate over ultra-thin body planar InGaAs quantum well field effect transistors with high-K gate dielectric and scaled gate-to-drain/gate-to-source separation; 2011 IEEE International Electron Devices Meeting (IEDM), Washington DC, Dec 5–7, 2011; IEEE: Bellingham, WA, 2011; pp 33.1. 1–33.1. 4.

(19) Azize, M.; Hsu, A. L.; Saadat, O. I.; Smith, M.; Xiang, G.; Shiping, G.; Gradecak, S.; Palacios, T. *IEEE Electron Device Lett.* **2011**, 32 (12), 1680–1682.

(20) Fortuna, S. A.; Li, X. IEEE Electron Device Lett. 2009, 30 (6), 593-595.

(21) Zota, C.; Wernersson, L.-E.; Lind, E. *IEEE Electron Device Lett.* 2014, 35 (3), 342–344.

(22) Hiruma, K.; Yazawa, M.; Katsuyama, T.; Ogawa, K.; Haraguchi, K.; Koguchi, M.; Kakibayashi, H. J. Appl. Phys. **1995**, 77 (2), 447–462.

- (23) Fan, Z.; Ho, J. C.; Jacobson, Z. A.; Yerushalmi, R.; Alley, R. L.; Razavi, H.; Javey, A. *Nano Lett.* **2008**, 8 (1), 20–25.

- (24) Duan, X.; Huang, Y.; Cui, Y.; Wang, J.; Lieber, C. M. Nature **2001**, 409 (6816), 66–69.

- (25) Yu, G.; Cao, A.; Lieber, C. M. Nat. Nanotechnol. 2007, 2 (6), 372–377.

- (26) Yao, J.; Yan, H.; Lieber, C. M. Nat. Nanotechnol. 2013, 8 (5), 329–335.

- (27) Javey, A.; Nam, S.; Friedman, R. S.; Yan, H.; Lieber, C. M. Nano Lett. 2007, 7 (3), 773–777.

- (28) Whang, D.; Jin, S.; Wu, Y.; Lieber, C. M. Nano Lett. 2003, 3 (9), 1255–1259.

- (29) Salalha, W.; Zussman, E. Phys Fluids 2005, 17 (6), 063301.

- (30) Oh, K.; Chung, J.-H.; Riley, J. J.; Liu, Y.; Liu, W. K. Langmuir 2007, 23 (23), 11932–11940.

- (31) Liu, Y.; Chung, J.-H.; Liu, W. K.; Ruoff, R. S. J. Phys. Chem. B 2006, 110 (29), 14098-14106.

- (32) Smith, B. D.; Mayer, T. S.; Keating, C. D. Annu. Rev. Phys. Chem. 2012, 63, 241–263.

- (33) Takahashi, T.; Takei, K.; Adabi, E.; Fan, Z.; Niknejad, A. M.; Javey, A. ACS Nano 2010, 4 (10), 5855–5860.

- (34) Fortuna, S. A.; Wen, J.; Chun, I. S.; Li, X. Nano Lett. 2008, 8 (12), 4421–4427.

- (35) Miao, X.; Li, X. IEEE Electron Device Lett. 2011, 32 (9), 1227–1229.

- (36) Dowdy, R.; Walko, D. A.; Fortuna, S. A.; Li, X. *IEEE Electron Device Lett.* **2012**, 33 (4), 522–524.

- (37) Miao, X.; Zhang, C.; Li, X. Nano Lett. 2013, 13 (6), 2548–2552.

(38) Zhang, C.; Li, X. Solid-State Electron. 2014, 93, 40–42.

- (39) Schvartzman, M.; Tsivion, D.; Mahalu, D.; Raslin, O.; Joselevich,

- (39) Schwatzman, M.; ISHOH, D.; Mahadi, D.; Kashi, O.; Josefevich, E. Proc. Natl. Acad. Sci. U.S.A. 2013, 110 (38), 15195–15200.

- (40) Nikoobakht, B.; Herzing, A. ACS Nano 2010, 4 (10), 5877–5886.

- (41) Yu, J.-W.; Li, C.-K.; Chen, C.-Y.; Wu, Y.-R.; Chou, L.-J.; Peng, L.-H. Appl. Phys. Lett. 2011, 99 (15), 152108-152108-3.

- (42) Dowdy, R. S.; Walko, D. A.; Li, X. Nanotechnology 2013, 24 (3), 035304.

- (43) Steiner, M.; Engel, M.; Yu-Ming, L.; Yanqing, W.; Jenkins, K.; Farmer, D. B.; Humes, J. J.; Yoder, N. L.; Seo, J.-W. T.; Green, A. A.; Hersam, M. C.; Krupke, R.; Avouris, P. *Appl. Phys. Lett.* **2012**, *101* (5), 053123–4.

- (44) Guo, Z.; Dong, R.; Chakraborty, P. S.; Lourenco, N.; Palmer, J.; Hu, Y.; Ruan, M.; Hankinson, J.; Kunc, J.; Cressler, J. D. *Nano Lett.* **2013**, *13* (3), 942–947.

- (45) Che, Y.; Lin, Y.-C.; Kim, P.; Zhou, C. ACS Nano 2013, 7 (5), 4343-4350.

- (46) Guillorn, M.; Chang, J.; Bryant, A.; Fuller, N.; Dokumaci, O.; Wang, X.; Newbury, J.; Babich, K.; Ott, J.; Haran, B. In *FinFET performance advantage at 22nm: An AC perspective*; 2008 Symposium on VLSI Technology, Honolulu, HI, June 17–19, 2008; IEEE: Bellingham, WA, 2008; pp 12–13.

- (47) Zhang, C.; Miao, X.; Mohseni, P. K.; Choi, W.; Li, X. Sitecontrolled VLS Growth of Planar Nanowires: Yield and Mechanism. *Nano Lett.* **2014**, *14* (12), 6836–6841.